xilinx一级代理_基于赛灵思 FPGA广泛应用于ASIC前端验证导读:本文概述了Xilinx XC7V系列FPGA在ASIC前端验证方面遇到的问题。记录并分享给您。如果有任何歧义或错误,请在评论中注明。

xilinx一级代理_基于赛灵思 FPGA广泛应用于ASIC前端验证

使用FPGA进行ASIC验证和实现传统RTL设计的主要区别在于ASIC具有大量门控时钟(clokc门)和功率门,具体取决于应用场景。电源门不需要在FPGA上实现,也无法实现。实现,它是由IP提供商或代工厂提供的源库和基本库文件,它是不可集成的类型。前端仿真将具有相应的仿真模型。当然,这种模型无法在FPGA上实现。时钟门,门控时钟,也有相应的仿真模型,可以通过一点修改在FPGA上合成和实现。

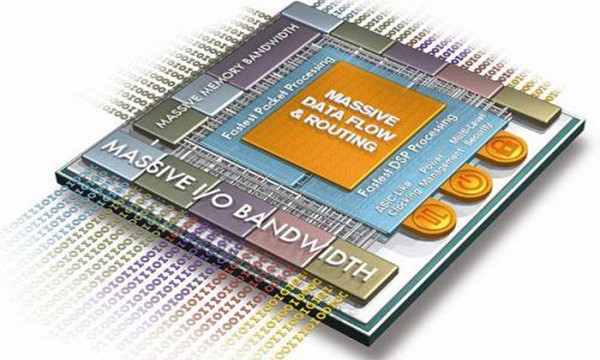

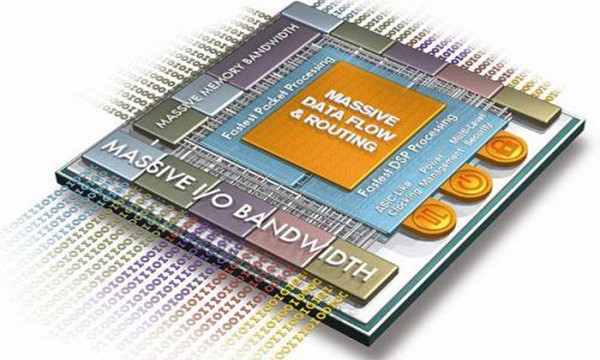

FPGA本身具有专用时钟单元。以xilinx FPGA为例,它是原始库中的BUFG。当使用BUFG时,FPGA工具可以确保时钟树到每个触发器的时钟输入C的路径相对相等,这可以有效地确保Clk_skew在合理的值内,因此“集成 - 优化 - 布局” - 接线过程“,保持基本没有问题,我们只需要集中精力解决设置的问题。在xilinx FPGA上BUFG资源有限且有价值,因此传统的FPGA设计需要代码来避免门控时钟,并且时钟域划分得非常清晰和干净,因此整个设计可以作为同步时钟工作,这将有利于TIming。收敛。

基于Xilinx FPGA的ASIC前端验证问题综述

但是,当FPGA用于实现ASIC验证时,门控时钟是不可避免的。例如,当ASIC通电时,并非所有逻辑同时工作,也就是说,只有触发器的一部分开始工作,并且很大一部分可能根本不存在。接收有效时钟,这种情况符合ASIC上电启动过程,因此在FPGA上进行验证时应保留;如果ASIC在某种情况下工作,它需要降低功耗,它将关闭模块的时钟。

可以直接优化存在的用于降低功耗的时钟门,而不会影响FPGA验证ASIC的功能。因此,在获得ASIC RTL之后,您必须首先选择可以优化的时钟门并对其进行处理,然后合成处理后的RTL以查看各种资源的使用是否合理。

LUT,FF,RAM等FPGA容量限制没有问题没问题。当然,在使用率特别高的情况下,PR速度将很慢并且存在失败的风险。 RTL可以根据需要进行定制。应检查BUFG的使用。 XC7V系列FPGA单芯片BUFG不超过32,而XC7V2000T多芯片FPGA将具有32x4 BUFG,但是当使用BUFG时,BUFG的使用尽可能小。很长一段时间,可能会在放置时报告错误,并且应逐个分析各种时钟之间的关系,这是一个跨时钟域问题。

1.内部报告是单时钟内部设置和保持问题。通常只会出现设置问题。如果存在保持问题,则应检查时钟代码是否使用了错误的BUFG,这会导致时钟偏差过大。当出现设置问题时,您可以查看关键路径。如果逻辑级别层是合理的,但数据路径延迟非常大,导致设置不可满足,则必须打开vivado布局工具并找到明显不合理的跟踪。

如果两个LUT之间的空间非常接近,则走线的延迟非常大,例如超过2 ns,那么这条走线很可能会进行冗余绕组,当然,这就是布线工具本身,这个绕组线路的目的可能是因为此路径仍然存在于另一个时钟时序约束中,这可能是跨时钟域的情况,因此您可以先忽略此设置的违规,但如果逻辑级别本身很大,例如已超过60,但你的路径时钟需要运行到80M,那么很难满足要求,翻过来看RTL问题,较好修改RTL,增加节拍;

2.报告间显示所有跨时域问题。通常,第一轮公关获得的国际举报违规行为将非常糟糕。您不必查看每个路径,但必须查看报告违规的每两个时钟。只能查看较严重违规的路径,首先检查工具所需的设置时间是否合理,因为我们没有对这两个时钟施加约束,所以这里的检查是较严格的,工具将遵循时钟。然后,找到延迟较小的两个上升沿来检查设置问题。如果延迟目标不合理,我们可以增加多周期约束。此延迟目标可能非常小,仅为几ns。